Advanced process and design techniques can also present daunting challenges when the chips are designed to meet often inconsistent specifications. In nanoscale designs, power consumption has become a major factor limiting performance. The materials and structures used in nanofabrication are extremely prone to increase leakage power and reduce heat transfer.

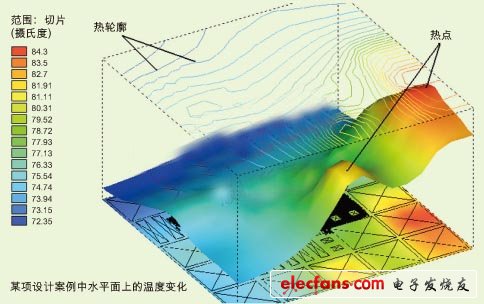

The net result of all these effects is a significant increase in power and temperature variations on the die. Boundary analysis methods based on uniform chip temperature have not guaranteed successful design convergence.

Temperature variations on the die can significantly affect chip power consumption, speed, and reliability. In particular, the leakage power is exponentially related to temperature, and if not handled properly, it will cause thermal runaway. Performance factors such as voltage drop and clock skew are also particularly susceptible to changes in space temperature and result in performance degradation.

Temperature also plays an important role in device performance degradation due to instability of the bias temperature, which is more noticeable in analog circuits. The cooling efficiency of the final package and associated cooling system can be reduced due to hot spots on the die. In many cases, the on-chip thermal sensor needs to be placed correctly in the highest temperature area.

Here are some of the heat-conscious design techniques. The accuracy of current design tools and processes can be improved by taking into account the temperature distribution across the die.

Suggest

1. Detect and eliminate hot spots in the design by thermal analysis as early as possible. It is important to understand the physical layout and power consumption as early as the underlying planning phase, which is also an excellent time for early thermal planning.

2. Consider packaging and metallization effects when developing thermal images of the die. Ignoring these structures, using power or power density maps to estimate temperature, can lead to inaccurate power estimates and other temperature-sensitive analysis results.

3. Carefully check the thermal effects during each design iteration phase that may change the chip power distribution. Thermal analysis performed in some important modes of operation of the device is usually sufficient to provide feedback on hotspots and other concerns.

4. Make full use of dispersed temperature information in clock trees and critical network designs that are sensitive to on-chip changes. Timing and signal integrity analysis will also benefit from accurate temperature and pressure drop information.

5. Design a thermal management system such as an on-chip thermal sensor and have a good thermal image of the die. If the sensors are placed in an incorrect position, they may not capture the highest temperature of the die and may result in overly optimistic feedback.

Figure: Temperature change on a horizontal plane in a design case

1. Calculate the maximum temperature of the die using a single supply value and a single QJA value of the package. This temperature value is usually too optimistic to know the hot spot effect on the die.

2. Estimate power and voltage drops without considering local temperature changes. The leakage power, which is a major component of total power, is exponentially related to temperature, and a small change in temperature can also cause a large change in leakage power. This power change also causes a significant change in the voltage drop across the power line.

3. Check the timing performance of the chip using a boundary analysis tool premised on a single uniform die temperature. Temperature differences above 10 °C plus the pressure drop changes described above will result in significant changes in cell delay. In addition, the increasingly obvious delay inversion effect can also cause problems in setup time analysis.

4. Perform reliability analysis without considering the temperature variation along the metal interconnect. The average downtime of the traces is exponentially related to temperature, which can lead to overly optimistic design, causing the product to fail prematurely on site.

5. Design the chip package without checking the presence and number of hot spots on the die. Hot spots can seriously affect the efficiency of the cooling material, resulting in excessive operating temperatures on the device.

Light reflectors in China with resonable price and good quality,We hope to establish cooperative relationship with you.

Light Reflector,Aluminum Light Reflector,Street Light Reflector,Energy Save Light Reflector

Yangzhou Huadong Can Illuminations Mould Manufactory Co., Ltd. , https://www.light-reflectors.com