This article refers to the address: http://

Since entering the Internet era, the huge information flow has brought about the richness of human culture and the trouble of storing information. In particular, the huge amount of data in video information has spawned the demand for video compression technology. Video compression technology has become one of the most popular technologies in the multimedia era, and is widely used in the fields of image transmission and storage such as television, movies, video telephony, video conferencing, and remote monitoring.H.264 video compression principle

From an information theory point of view, the image as a source, the data describing the source is the sum of the amount of information (source entropy) and the amount of information redundancy. There are many kinds of information redundancy, such as spatial redundancy, time redundancy, structural redundancy, knowledge redundancy, visual redundancy, etc. Data compression essentially reduces these redundancy. It can be seen that the reduction in redundancy can reduce the amount of data without reducing the amount of information of the source. Mathematically, an image can be thought of as a multidimensional function, and compressing the amount of data describing the function essentially reduces its correlation.

According to the constituent elements of image information, H.264 adopts intra prediction, inter prediction, motion estimation and motion compensation, integer transformation, etc. to improve the compression ratio of the image. Where intra prediction is H.264 based on the similarity of adjacent pixels in the image, using the correlation of adjacent pixels, adopting a new intra prediction mode, passing the left and upper pixels of the current pixel block (encoded reconstructed Pixel) performs prediction, encoding only the difference between the actual value and the predicted value, so that the intra-coded pixel block information can be expressed with a smaller number of bits; and the inter-frame prediction passes the multi-frame reference and the smaller motion prediction region. The method can accurately predict the next frame, thereby reducing the amount of data transmitted and reducing the time domain correlation of the image. H.264 transforms the residual results of motion estimation and intra prediction from the time domain to the frequency domain, using integer transforms similar to 4×4 discrete cosine transform (DCT) instead of MPEG-2 and MPEG-4. That uses a floating point number conversion of 8 x 8 DCT. Integer-based spatial transformation has good effect, fast calculation (only addition and shift operation), no adaptation problem in the inverse transformation process, and combined with the quantization process to ensure that in the 16-bit computing system, The result of the calculation has the highest precision and does not overflow. The 4×4 transform block is also 8×8, which can reduce the blockiness and the ringing effect.

How Hi3510 works

Hi3510 is a video compression chip based on H.264 BP algorithm launched by HiSilicon. The chip adopts multi-core and highly integrated SoC architecture of ARM+DSP+ hardware acceleration engine and has powerful video processing functions. Real-time encoding performance of DVD quality, adaptive to various network environments, ensuring picture clarity and real-time performance, low-rate H.264 encoding technology greatly reduces network storage space, and integrates DES/3DES Decrypt the hardware engine to ensure network security. Hi3510 adopts 0.13μm process, LFBGA400 package, size 19×19mm, pin pitch is 0.8mm, and integrates digital video interface, USB, ETH, I2S, I2C, GPIO, SPI, UART, SDRAM, DDR and other interfaces. The device development that satisfies various application scenarios can greatly reduce the BOM cost of the device.

Hi3510 works: The video input unit receives the digital video information output by the VADC through the ITU-R BT.601/656 interface, and writes the received original image to the external memory (SDR SDRAM or DDR SDRAM) through the AHB bus. Video codec reads images from external memory for motion estimation (inter prediction), intra prediction, DCT transform, quantization, entropy coding (CAVLC+Exp-Golomb), IDCT transform, inverse quantization, motion compensation, etc. Operation, finally writing the naked code stream conforming to the H.264 protocol and the coded reconstructed frame (as the reference frame of the next frame) into the external memory; the video output unit reads the image from the external memory and passes the ITU-R BT The .601/656 interface is sent to the VDAC for display. The application requirements are different. The video output unit reads the image content from the external memory. When the input image needs to be previewed, the video output unit reads the original from the external memory. Image, when it is necessary to observe the encoding effect of the video encoder, the video output unit reads the encoded reconstructed frame from the external memory; the ARM encodes the code stream output by the video encoder into a protocol stack, and then sends the network port to send, to implement Video on demand business.

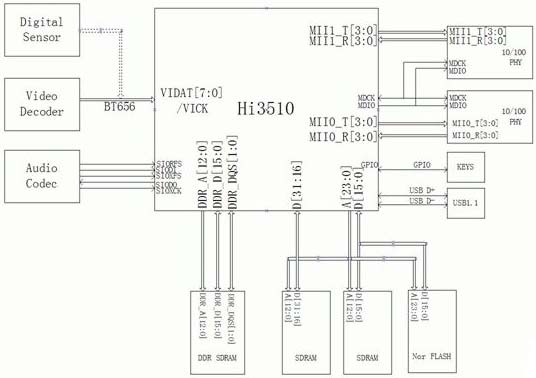

As shown in Figure 1, the chip consists of the core of ARM+DSP+video codec accelerator+graphic engine scaler, integrates a rich peripheral interface, and integrates internally, such as digital watermarking and DES/3DES algorithms, so that the single chip can adapt to the basics. All the work, reducing the development difficulty with other chips, but also eliminating the need for manufacturers to repeat the development of the standard part of the algorithm, greatly reducing the investment threshold of equipment manufacturers. With the development kits of different application forms of HiSili, you can develop various products such as PMP, videophone, network monitoring, PVR, video intercom and so on.

Figure 1: Logical block diagram of Hi3510 H.264 audio and video codec SoC.

Implementation of Hi3510 codec scheme

As a codec chip for the SoC architecture, the Hi3510 is designed with compatibility and ease of use in mind. Supports a range of AD/DA chips produced by almost all companies. The Hi3510 can work as a stand-alone encoder, as an independent decoder, or as a codec at the same time, taking into account the various applications in the codec market. The Hi3510 is a typical multi-application single-chip solution that greatly reduces the BOM composition and cost of the device. Figure 2 shows the application of chip simultaneous codec.

Figure 2: The Hi3510 is a typical multi-application single-chip solution.

Application of i3510 codec

The Hi3510 comes with a Linux operating system (supporting Vxworks, WinCE and other open operating systems) and an ARM processor, which enables the chip to implement many rich application functions in addition to the codec function. As shown in Figure 2, the function of digitizing, compressing, and storing and transmitting composite video signals can be realized by adding a single AD. The Hi3510 development kit provides an upper API interface that enables you to implement all of the chip functions and develop your own personalization capabilities. Figure 3 shows the application design of the chip's encoding scheme.

Figure 3: Application design of the Hi3510 chip coding scheme.

The decoder application is the same in architecture design as the encoder (convenient solution can maintain consistency, can achieve a set of hardware to meet the requirements, only software upgrades). The decoder only needs to be equipped with a DA chip (if the LCD digital screen can save the chip), the decoding of the data stream can be realized, and the menu operation of the user and the human-machine interaction can be realized through the GUI or the OSD, and the PMP and the like can be realized. Applications. Figure 4 shows the application design of the chip's decoding scheme.

Figure 4: Application design of the Hi3510 chip decoding scheme.

Summary of this article

The application of the H.264 standard provides technical support for video network transmission, especially for low bandwidth (such as wireless transmission). In today's information explosion, the market requires designers to launch products faster and faster, and in order to maintain product competitiveness, to maintain sufficient advantages in product prices, product application features, especially in the multimedia market. Based on the standard algorithm, HiSilicon's SoC chip gives designers maximum flexibility to design the right products, which greatly reduces the input cost of the manufacturer, shortens the time for the manufacturer to launch new products, and prepares to win the market. .

Wood Burning Stove is a direct combustion of dead leaves eliminated in the natural environment, leaving almost no residue after burning, only a small amount of white ashes, the planet of our existence has played a maximum of care.The actual use of metal skin in the ordinary home firewood stove wall adds a layer of air duct (convenient, then cut steel pipe can be used instead) around the bottom of the flame for oxygen supplemental combustion, the key is to use the thick hearth furnace production, the thicker The better, so that the top of the flame heat will be able to spread to the bottom of the bottom of the gasification of the decomposition of combustible gas, which is the same principle with the gasifier, because it is dependent on iron heat transfer, solid from top to bottom Iron hearth temperature is gradually decreased, so the firewood will burn down from the top.

Wood Stove, Wood Burning Stove, Camping Wood Stove, APG Camping Wood Stove, Wood Floding Stove

Ningbo APG Machine(appliance)Co.,Ltd , http://www.apgelectrical.com