A DMA controller is a unique peripheral that transfers data inside the system and can be thought of as a controller that can connect internal and external memory to each DMA-capable peripheral through a dedicated bus. It belongs to the peripheral because it is transmitted under the program control of the processor.

Transmission structure and settingsThere are currently two main types of DMA transfer structures: register mode and descriptor mode. Regardless of the type of DMA, several of the information in Table 1 will appear in the DMA controller. When the DMA is operating in register mode, the DMA controller simply uses the parameter values ​​stored in the registers. In descriptor mode, the DMA controller looks up its own configuration parameters in memory.

(1) Register-based DMA

Inside the register-based DMA, the processor directly programs the DMA control registers to initiate the transfer. Register-based DMA provides the best DMA controller performance because registers do not need to constantly load data from descriptors in memory, and the kernel does not need to maintain descriptors. Register-based DMA consists of two sub-modes: Autobuffer mode and Stop mode. In the auto-buffered DMA, when a transfer block is transferred, the control register automatically reloads its initial set value, and the same DMA process is restarted with zero overhead. If an auto-buffer DMA is set to transfer a certain number of words from the peripheral to the buffer of the L1 data memory, the DMA controller will quickly reload the initial parameters at the end of the last word transfer. This constitutes a "loop buffer" because when a value is written to the last position of the buffer, the next value will be written to the first position of the buffer.

Auto-buffered DMA is especially well-suited for performance-sensitive applications that have continuous data streams. The DMA controller can read in the data stream independently of other processor activity and then issue an interrupt to the core at the end of each transfer.

The stop mode works like the auto-buffer DMA, except that each register does not reload after the DMA is finished, so the entire DMA transfer only happens once. Stop mode is useful for one-time transfers based on certain events. For example, non-periodical transfer of data blocks from one location to another. This mode is also very useful when you need to synchronize events. For example, if a task must be completed before the next transfer, the stop mode ensures the order in which events occur. In addition, the stop mode is very useful for buffer initialization.

(2) Descriptor model

Descriptor-based DMA requires storing a set of parameters in memory to initiate a series of DMA operations. The descriptor contains the same parameters as those normally programmed into the DMA control register set. However, the descriptor can also allow multiple DMA operation sequences to be strung together. In descriptor-based DMA operations, we can program a DMA channel to automatically set up and start another DMA transfer after the current sequence of operations is completed. The descriptor-based approach provides maximum flexibility for managing DMA transfers in the system.

basic component(1) Memory address counter: The address used to store the data to be exchanged in the memory. Before the DMA transfer, the data must be sent to the memory address counter by the program in the starting position (first address) in the memory. When the DMA transfers, the address counter is incremented by "1" every time the data is exchanged, thereby giving the address of a batch of data to be exchanged in the memory incrementally.

(2) Word counter: used to record the length of the transmitted data block (how many words). The content is also preset by the program before data transfer, and the number of words exchanged is usually expressed in complement form. At the time of DMA transfer, the word counter is incremented by "1" for each word transmitted. When the counter overflows, the highest bit generates a carry, indicating that the batch of data is transferred, thus causing the DMA controller to send an interrupt signal to the CPU.

(3) Data buffer register: used to temporarily store data (one word) for each transfer. When input, it is sent to the data buffer register by the device (such as a disk), and then sent to the memory by the buffer register through the data bus. Conversely, when outputting, the memory is sent to the data buffer register through the data bus and then sent to the device.

(4) DMA request" flag: A control signal is given every time the device prepares a data word to make "DMA"

The request flag is set to "1". When this flag is set, a DMA request is issued to the "control/status" logic, which in turn issues a bus usage right request (HOLD) to the CPU, and the CPU sends back a response signal HLDA in response to the request. The Control/Status logic receives this signal and issues a DMA response to reset the DMA Request flag in preparation for swapping the next word.

(5) Control/Status logic: consists of control and timing circuits and status flags, etc., used to modify the memory address counter and word counter, specify the transfer type (input or output), and the "DMA request" signal and CPU response signal. Coordinate and synchronize.

(6) Interrupt mechanism: When the word counter overflows, it means that a group of data is exchanged, the interrupt mechanism is triggered by the overflow signal, and an interrupt report is reported to the CPU.

Second, Nios II introductionThe Nios II embedded processor is ALTERA's second-generation on-chip programmable soft-core processor with a 32-bit instruction set using Harvard architecture. Its biggest advantage and feature is the modular hardware structure and the resulting Flexibility and slashability.

NiosII featuresThe Nios II family supports the use of dedicated instructions. Dedicated instructions are user-added hardware modules that add an arithmetic logic unit (ALU). Users can create up to 256 dedicated instructions for each Nios II processor used in the system, allowing designers to fine-tune system hardware to meet performance goals. The dedicated instruction logic is identical to its own Nios II instruction and can take values ​​from up to two source registers and optionally write the result back to the destination register. At the same time, the Nios II family supports more than 60 peripheral options, allowing developers to select the right peripherals for the most appropriate combination of processors, peripherals and interfaces without having to pay for the silicon features that are not used at all. The Nios II family can meet the needs of any application 32-bit embedded microprocessor. Customers can migrate the first generation Nios processor design to a Nios II processor. Altera will support the first generation of Nios on the existing FPGA family. processor. In addition, Altera offers a one-click migration option that can be upgraded to the Nios II family. The Nios II processor can also be implemented in HardCopy devices, and Altera also provides an ASIC migration method for Nios II processor-based systems.

Development environmentThe Nios II processor has a comprehensive software development kit that includes a compiler, integrated development environment (IDE), JTAG debugger, real-time operating system (RTOS), and TCP/IP stack. Designers can easily create dedicated processor systems using the SOPC Builder system development tools in Altera's Quartus II development software, and can add the number of Nios II processor cores to the needs of the system.

Use the Nios II software development tool to build software for the Nios II system, which is a one-click automatic generation of a dedicated C/C++ runtime environment for system hardware. The Nios II Integrated Development Environment (IDE) provides a number of software templates that simplify project setup. In addition, the Nios II development kit includes two third-party real-time operating systems (RTOS)—MicroC/OS-II (Micrium), Nucleus Plus (ATI/Mentor), and the TCP/IP stack for network applications.

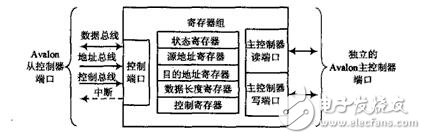

Third, the principle and application of DMA controller in Nios II system 1. Principle of dma controller 1.1dma function introductionThe dma controller in nios ii consists of two avalon-mm type master controller ports (read port and write port), one for dma control avalon-mm type slave port and some internal register groups, its structure Figure is shown in Figure 1.

Figure 1. Structure of the dma controller The dma controller can move data from the source address to the destination address. The source address or destination address can be a range of addresses in memory or a peripheral of the avalon slave controller. Therefore, in the nios ii system, there are three types of dma operations, namely memory to peripherals, peripheral to memory, and memory to memory. The dma controller also has streaming capabilities that allow for fixed or variable length data transfers. When the dma operation ends, the dma controller issues an interrupt (irq) request. The typical dma data transmission process is as follows:

(1) The cpu configures the dma controller for data transmission by writing to the control port;

(2) The dma controller sends a hold signal to the cpu to request the occupation of the bus;

(3) The cpu responds to the request of the dma controller and gives up the bus, and the dma controller obtains the control of the bus;

(4) The dma controller read port reads data from the source address, the write port writes data to the destination address, and the read and write ports use fifo to cache data;

(5) When the specified data is transmitted, the dma transmission ends and an interrupt request is issued to the nios ii cpu;

(6) The cpu responds to the interrupt request, and dma surrenders the bus control.

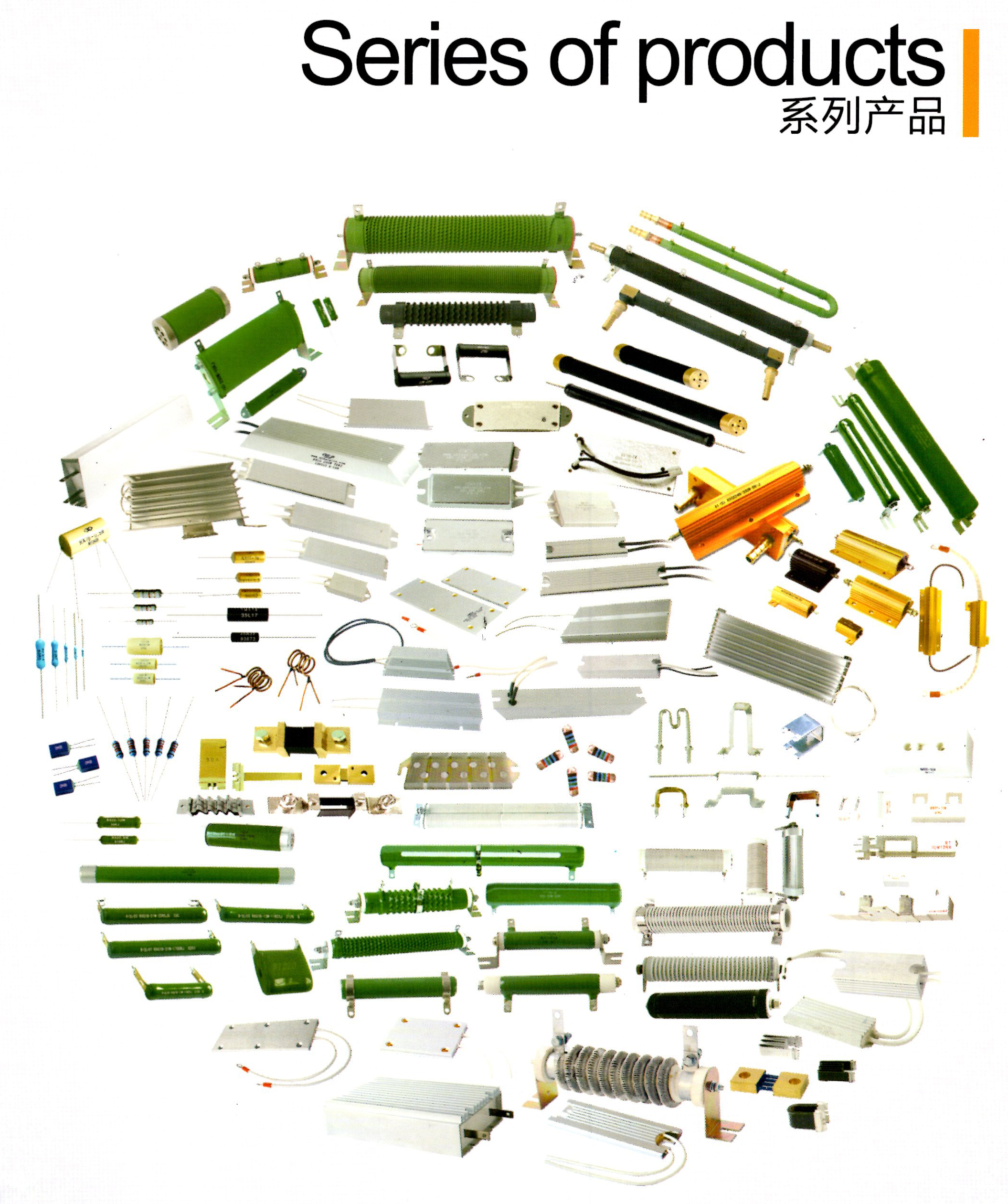

Electronic Components Resistor

Resistor (Resistor) commonly known as resistance directly in our daily life.It is a current limiting element. When the resistance is connected to the circuit, the resistance value of the resistor is fixed, usually two pins.Fixed resistors are those whose resistances cannot be changed.Resistance variable is called potentiometer or variable resistor.The ideal resistor is linear, that is, the instantaneous current through the resistor is proportional to the applied instantaneous voltage.Variable resistor for partial pressure.On the exposed resistor body, one or two movable metal contacts are pressed tightly.The contact position determines the resistance between any end of the resistance body and the contact.

Flat tube resistor

Metal aluminum shell resistor

Stainless steel resistor box

Crowbar (wind power converter) resistor

RX21 Glazed Wirewound Resistor

RX21 Glazed Power Wirewound Resistor

Inverter ceramic resistor

Resistor Cabinet

Resistive load box

Ultra-thin aluminum shell resistor

High power resistor

water cooling resistor

RI80 high voltage resistor

RX20 High Power Painted Wirewound Resistor

stainless steel resistor

Howo resistor

KNP Porcelain Rod Painted Wirewound Resistor

Cement Resistor

Thick Film Resistors

Electronic Components Resistor,Metal Film Resistor,Metal Oxide Film Resistor

YANGZHOU POSITIONING TECH CO., LTD. , https://www.cnchipmicro.com