With the development of electronic technology, VGA ( Video Graphics Array) interface appears on many embedded platforms for real-time display of image information. In some cases, the designer wants to observe some vector signals inside the FPGA through a common display or projector, that is, use the display with VGA interface as an oscilloscope, etc., which requires processing the data so that it can be displayed on the display. Displayed in real time.

Based on DSP Builder 's VGA interface design method, this paper introduces the VGA interface timing and system design requirements, and realizes the display of 1D and 2D signals under the hardware platform.

VGA interface standard

VGA imaging principle

The display is scanned by raster scanning, and the electron beam is regularly scanned from left to right and top to bottom on the display screen. During the scanning process, it is controlled by the line synchronization signal, sweeping to the right point by point, and the reciprocal of the time of completing one line of scanning is the line frequency; at the same time, returning to the left end of the screen during the line synchronization pulse period, forming a frame from top to bottom, The vertical direction is controlled by the field sync signal, and the time reciprocal of one frame is the field frequency. The display process of the image is that the address is corresponding to the pixels of the image in the process of electron beam scanning, and each of the addressed pixels obtains only its own control information, and does not interfere with the surrounding pixels, so that the display can be stable. Image.

The VGA interface is an interface for outputting analog signals on the display card, also called D-Sub interface. This interface has a total of 15 pinholes, divided into 3 rows, 5 per row, through the analog VGA interface to display the working principle of the image, the digital display image information generated inside the computer, through the ADC in the graphics card into R, The G and B primary color signals and the line and field sync signals are transmitted to the display device through the cable.

VGA timing

The timing of the VGA includes horizontal timing and vertical timing, and both contain timing parameters: horizontal (vertical) sync pulse, width between the end of the horizontal (vertical) sync pulse to the beginning of the effective display data area (back edge), valid The width of the display area, the end of the valid data display area to the start of the horizontal (vertical) sync pulse width (leading edge). The area where the horizontal effective display area width and the vertical effective display area width are logically connected is the visible area, and the other areas are the blanking area.

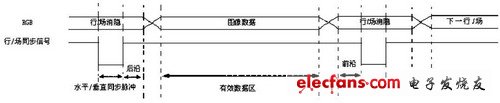

The timing information of a line or a field is shown in Figure 1.

Figure 1 row / field timing diagram

According to the current display performance parameters, the LG 505E is taken as an example. The maximum resolution can reach 1024 & TImes; 768@60 Hz, the horizontal scanning frequency is 30 kHz to 54 kHz, the vertical scanning frequency is 50 Hz to 120 Hz, and the bandwidth is 75 MHz.

Design method of VGA interface based on DSP Builder

Features that need to be completed in this design include VGA timing and signal display based on the VGA interface. The interface system conforms to the VGA interface standard, and the one-dimensional vector signal and the two-dimensional image signal can be displayed under the system, and the integration of the system is embodied, and the interface is integrated into the SOPC system.

System clock determination

Calculate the formula based on the system clock:

Clock frequency = (number of rows of pixels + number of rows of blanking points) & TImes; (number of rows + number of blanking lines) & TImes; refresh rate.

For the standard VGA interface timing 640 & TImes; 480@60Hz, the clock frequency is 800 × 525 × 60 = 25.175MHz.

In this design, we use the XGA display mode of 1024×768@60Hz, so the clock frequency of the system is PixelClk=1344×806×60=64.99MHz.

State machine design

The finite state machine can be designed by the VGA timing to complete the timing signal. Taking the design of 1024×768@60Hz as an example, four states are designed for the line synchronization signal, that is, the line synchronization pulse signal area (horsync), the back edge area (backporch), and the data. Video and frontporch. The value of the counter hcnt is used to distinguish the signals of each stage, and the maximum value is 1344. The field sync signal is also designed in the above four states. When the scan of one line is completed, the field counter vcnt starts counting, so one field can have multiple lines.

VGA DAC chip and corresponding signal generation

A typical VGA DAC chip needs to input a corresponding driving signal to work, including a clock signal, a synchronization signal, an effective display area signal, and the like. The DAC chip used in the system is FMS3818, and its signals include clock and data signal (RGB) input, control signal input (sync and blank), and RGB signal DA output. The line sync and field sync signals are output to the VGA interface together with the RGB data signals generated by the VGA DAC to drive the CRT display. In this design, the clock signal is 65 MHz, the synchronization signal is generated by horsync and versync, and the effective display area signal is generated by the line and field effective data area signals.

One-dimensional vector signal display

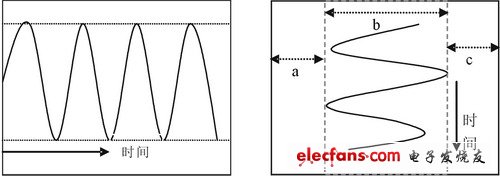

To display a one-dimensional vector signal in a two-dimensional space, the conventional display method may be to display a one-dimensional signal from left to right, as shown in Fig. 2(a), as observed on a conventional oscilloscope. Thus, in the VGA display, one line sweeps through multiple sampling points, and the position of the sampling point to be displayed needs to be calculated. When the line signal is swept, the value of the sampling point is assigned to the pixel point, and the signal display is completed. For continuous one-dimensional signals, the display method of Figure 2(b) is more reasonable because the horizontal frequency is higher than the field frequency. To this end, the time axis of the one-dimensional signal is mapped to the vertical direction, and the amplitude is mapped to the horizontal direction. When the line scan signal sweeps through one line, one sampling point of the one-dimensional signal is mapped, that is, one line of signals corresponds to one pixel, when completed A line of signals is then retraced and a line is scanned. Under normal circumstances, after the field frequency is determined, the number of cycles that can be displayed can be determined according to the frequency of the one-dimensional signal. When a signal is completed, one frame of image is displayed on the screen.

In the specific implementation, it is necessary to control the parameters of the one-dimensional sine wave signal by two points: control the frequency of the sine wave, ensure that one line scan corresponds to one sampling point; control the amplitude of the sine wave, and control it in the effective display area of ​​1024×768 in.

For a sine wave frequency, if the frequency is too high, one line will sweep to multiple sampling points; if the frequency is too low, a full screen cannot display a full cycle of signals. In this design, a lower sampling clock is used to control the sampling of the sine wave, which is stored in a lookup table. If n cycles of sinusoidal signals are to be displayed in one screen, then the required sampling frequency fs = refresh rate x n x points of one cycle in the lookup table.

Control the sine wave amplitude so that the maximum value of the sine wave cannot exceed the display area of ​​the screen. The VGA effective display width is 1024, and the width of the free portion at both ends of the screen (Figs. 2(a) and (c)) is 100.

(a) (b)

Figure 2 Schematic diagram of one-dimensional sine wave VGA display

How to display two-dimensional image signals

The display process of a two-dimensional image is easier to implement than a one-dimensional signal. For two-dimensional images, a two-dimensional image signal can be converted into a one-dimensional pixel sequence. In the screen display area, when the line and field sync signal is swept, the RGB value corresponding to the pixel is assigned, and the display of the two-dimensional image can be completed. For this design, the VGA timing is 1024×768 mode, and the number of pixels of the image can be completely displayed on the screen within this range without pixel loss. If the image is small, you can also control the image in any area of ​​the screen. Since the image size is limited by the storage space, if you want to achieve higher pixel images, you must borrow external SRAM or SDRAM for image caching.

Avalon MM interface control

In DSP Builder, Altera provides the interface between this design and SOPC - the Avalon MM interface.

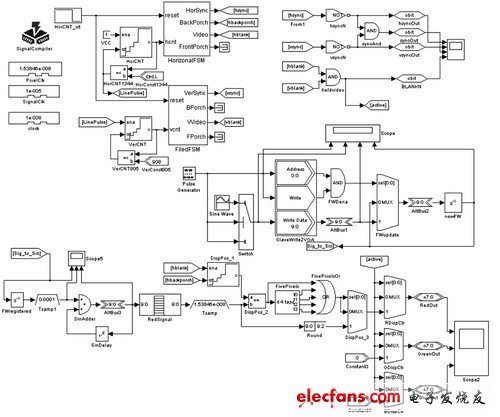

The interface signals defined by the Avalon MM interface mainly include chip select, read enable, write enable, address, and data. According to the logic of the peripheral, different interface definition signals are selected. Through these signals, the Avalon master (CPU) can write address and data signals to the slave peripherals hanging on the Avalon bus, and the Avalon master peripherals can also actively obtain the signals. Data in SRAM or SDRAM on the Avalon bus. Whether it is a master transfer or a transfer, it is necessary to meet the read and write timing of the Avalon bus to initiate a correct data transfer. Modules designed in DSP Builder can be made into custom peripherals using the Avalon MM interface. The Nios II CPU can use the Avalon bus to communicate with the custom peripherals generated in the DSP Builder. In this design, the address of the VGA interface integrated into the SOPC system is assigned 0x1, the data is written to 0x1, and the VGA interface controller receives When the data is reached, VGA timing information and RGB signals are generated according to the design, and the image is displayed on the screen. Figure 3 is a block diagram of the entire one-dimensional signal VGA display system.

Figure 3 system structure diagram

Simulation and hardware verification

This design is verified under the 2C70 DSP hardware development platform.

With the Signal Complier module in DSP Builder, the designed system can be easily converted into the RTL-level hardware description language, and the VGA timing verification and sine wave signal download and display can be completed under the Quartus II.

From the hardware simulation results on the display, the amplitude of the sine wave changes periodically in the effective display area. Therefore, when the display is connected to the J21 of the VGA port, the amplitude of the sine wave on the screen is displayed within the designed range, one screen. The number of cycles displayed is the same as that set in DSP Builder. On this basis, the sampling frequency of the sine wave can be adjusted, the display frequency and amplitude of the sine wave can be controlled, the function of the oscilloscope can be realized, and the signal inside the FPGA can be observed.

Conclusion

With the widespread use of the VGA interface, this system-level design approach combining FPGA and DSP Builder has demonstrated advantages. From the perspective of the entire design process, the system has strong flexibility, high reliability, greatly reduced design cycle, reduced cost, and strong system scalability. In the future, VGA interface image and video surveillance system applications will be very marketable. â–

we are the best supplier in China to offer the networking tools including sort of insertion tools, impact and punch down tool (Ericsson punch down tool, Siemens punch down tool, Corning punch down tool and so on), Crimping Tool(RJ45 crimping tools, coaxial Cable Crimping Tool, picabond ratchet crimper), cable stripper and cutter, Cable Tester and connector removal tool, and so on.

In short, we offer the networking tools for cutting and stripping coaxial cable, twist cable, and optical fiber. And professional compression crimping tool for different connectors, insertion tools for different modules .To save cost for customers, we have desired some tools with multi-function. So you can keep one tool instead of several different types. Meanwhile, for some coaxial cable crimping tool you can change the head to fit the cable specification yourself. It will make you lose weight on tool set but to finish your work perfectly.

Insertion Tool, Punch Tool, Cat 5 Cable Tester, Crimping Pliers, Cable Crimping Tool

NINGBO YULIANG TELECOM MUNICATIONS EQUIPMENT CO.,LTD. , https://www.yltelecom.com